канал ацп что это

Аналого-цифровое преобразование для начинающих

В этой статье рассмотрены основные вопросы, касающиеся принципа действия АЦП различных типов. При этом некоторые важные теоретические выкладки, касающиеся математического описания аналого-цифрового преобразования остались за рамками статьи, но приведены ссылки, по которым заинтересованный читатель сможет найти более глубокое рассмотрение теоретических аспектов работы АЦП. Таким образом, статья касается в большей степени понимания общих принципов функционирования АЦП, чем теоретического анализа их работы.

В качестве отправной точки дадим определение аналого-цифровому преобразованию. Аналого-цифровое преобразование – это процесс преобразования входной физической величины в ее числовое представление. Аналого-цифровой преобразователь – устройство, выполняющее такое преобразование. Формально, входной величиной АЦП может быть любая физическая величина – напряжение, ток, сопротивление, емкость, частота следования импульсов, угол поворота вала и т.п. Однако, для определенности, в дальнейшем под АЦП мы будем понимать исключительно преобразователи напряжение-код.

Понятие аналого-цифрового преобразования тесно связано с понятием измерения. Под измерением понимается процесс сравнения измеряемой величины с некоторым эталоном, при аналого-цифровом преобразовании происходит сравнение входной величины с некоторой опорной величиной (как правило, с опорным напряжением). Таким образом, аналого-цифровое преобразование может рассматриваться как измерение значения входного сигнала, и к нему применимы все понятия метрологии, такие, как погрешности измерения.

Основные характеристики АЦП

АЦП имеет множество характеристик, из которых основными можно назвать частоту преобразования и разрядность. Частота преобразования обычно выражается в отсчетах в секунду (samples per second, SPS), разрядность – в битах. Современные АЦП могут иметь разрядность до 24 бит и скорость преобразования до единиц GSPS (конечно, не одновременно). Чем выше скорость и разрядность, тем труднее получить требуемые характеристики, тем дороже и сложнее преобразователь. Скорость преобразования и разрядность связаны друг с другом определенным образом, и мы можем повысить эффективную разрядность преобразования, пожертвовав скоростью.

Существует множество типов АЦП, однако в рамках данной статьи мы ограничимся рассмотрением только следующих типов:

Наибольшим быстродействием и самой низкой разрядностью обладают АЦП прямого (параллельного) преобразования. Например, АЦП параллельного преобразования TLC5540 фирмы Texas Instruments обладает быстродействием 40MSPS при разрядности всего 8 бит. АЦП данного типа могут иметь скорость преобразования до 1 GSPS. Здесь можно отметить, что еще большим быстродействием обладают конвейерные АЦП (pipelined ADC), однако они являются комбинацией нескольких АЦП с меньшим быстродействием и их рассмотрение выходит за рамки данной статьи.

Среднюю нишу в ряду разрядность-скорость занимают АЦП последовательного приближения. Типичными значениями является разрядность 12-18 бит при частоте преобразования 100KSPS-1MSPS.

Наибольшей точности достигают сигма-дельта АЦП, имеющие разрядность до 24 бит включительно и скорость от единиц SPS до единиц KSPS.

Еще одним типом АЦП, который находил применение в недавнем прошлом, является интегрирующий АЦП. Интегрирующие АЦП в настоящее время практически полностью вытеснены другими типами АЦП, но могут встретиться в старых измерительных приборах.

АЦП прямого преобразования

АЦП прямого преобразования получили широкое распространение в 1960-1970 годах, и стали производиться в виде интегральных схем в 1980-х. Они часто используются в составе «конвейерных» АЦП (в данной статье не рассматриваются), и имеют разрядность 6-8 бит при скорости до 1 GSPS.

Архитектура АЦП прямого преобразования изображена на рис. 1

Рис. 1. Структурная схема АЦП прямого преобразования

Принцип действия АЦП предельно прост: входной сигнал поступает одновременно на все «плюсовые» входы компараторов, а на «минусовые» подается ряд напряжений, получаемых из опорного путем деления резисторами R. Для схемы на рис. 1 этот ряд будет таким: (1/16, 3/16, 5/16, 7/16, 9/16, 11/16, 13/16) Uref, где Uref – опорное напряжение АЦП.

Пусть на вход АЦП подается напряжение, равное 1/2 Uref. Тогда сработают первые 4 компаратора (если считать снизу), и на их выходах появятся логические единицы. Приоритетный шифратор (priority encoder) сформирует из «столбца» единиц двоичный код, который фиксируется выходным регистром.

Теперь становятся понятны достоинства и недостатки такого преобразователя. Все компараторы работают параллельно, время задержки схемы равно времени задержки в одном компараторе плюс время задержки в шифраторе. Компаратор и шифратор можно сделать очень быстрыми, в итоге вся схема имеет очень высокое быстродействие.

Но для получения N разрядов нужно 2^N компараторов (и сложность шифратора тоже растет как 2^N). Схема на рис. 1. содержит 8 компараторов и имеет 3 разряда, для получения 8 разрядов нужно уже 256 компараторов, для 10 разрядов – 1024 компаратора, для 24-битного АЦП их понадобилось бы свыше 16 млн. Однако таких высот техника еще не достигла.

АЦП последовательного приближения

АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий еще к Фибоначчи. В своей книге «Liber Abaci» (1202 г.) Фибоначчи рассмотрел «задачу о выборе наилучшей системы гирь», то есть о нахождении такого ряда весов гирь, который бы требовал для нахождения веса предмета минимального количества взвешиваний на рычажных весах. Решением этой задачи является «двоичный» набор гирь. Подробнее о задаче Фибоначчи можно прочитать, например, здесь: http://www.goldenmuseum.com/2015AMT_rus.html.

Аналого-цифровой преобразователь последовательного приближения (SAR, Successive Approximation Register) измеряет величину входного сигнала, осуществляя ряд последовательных «взвешиваний», то есть сравнений величины входного напряжения с рядом величин, генерируемых следующим образом:

1. на первом шаге на выходе встроенного цифро-аналогового преобразователя устанавливается величина, равная 1/2Uref (здесь и далее мы предполагаем, что сигнал находится в интервале (0 – Uref).

2. если сигнал больше этой величины, то он сравнивается с напряжением, лежащим посередине оставшегося интервала, т.е., в данном случае, 3/4Uref. Если сигнал меньше установленного уровня, то следующее сравнение будет производиться с меньшей половиной оставшегося интервала (т.е. с уровнем 1/4Uref).

3. Шаг 2 повторяется N раз. Таким образом, N сравнений («взвешиваний») порождает N бит результата.

Рис. 2. Структурная схема АЦП последовательного приближения.

Таким образом, АЦП последовательного приближения состоит из следующих узлов:

1. Компаратор. Он сравнивает входную величину и текущее значение «весового» напряжения (на рис. 2. обозначен треугольником).

2. Цифро-аналоговый преобразователь (Digital to Analog Converter, DAC). Он генерирует «весовое» значение напряжения на основе поступающего на вход цифрового кода.

3. Регистр последовательного приближения (Successive Approximation Register, SAR). Он осуществляет алгоритм последовательного приближения, генерируя текущее значение кода, подающегося на вход ЦАП. По его названию названа вся данная архитектура АЦП.

4. Схема выборки-хранения (Sample/Hold, S/H). Для работы данного АЦП принципиально важно, чтобы входное напряжение сохраняло неизменную величину в течение всего цикла преобразования. Однако «реальные» сигналы имеют свойство изменяться во времени. Схема выборки-хранения «запоминает» текущее значение аналогового сигнала, и сохраняет его неизменным на протяжении всего цикла работы устройства.

Достоинством устройства является относительно высокая скорость преобразования: время преобразования N-битного АЦП составляет N тактов. Точность преобразования ограничена точностью внутреннего ЦАП и может составлять 16-18 бит (сейчас стали появляться и 24-битные SAR ADC, например, AD7766 и AD7767).

И, наконец, самый интересный тип АЦП – сигма-дельта АЦП, иногда называемый в литературе АЦП с балансировкой заряда. Структурная схема сигма-дельта АЦП приведена на рис. 3.

Рис.3. Структурная схема сигма-дельта АЦП.

Принцип действия данного АЦП несколько более сложен, чем у других типов АЦП. Его суть в том, что входное напряжение сравнивается со значением напряжения, накопленным интегратором. На вход интегратора подаются импульсы положительной или отрицательной полярности, в зависимости от результата сравнения. Таким образом, данный АЦП представляет собой простую следящую систему: напряжение на выходе интегратора «отслеживает» входное напряжение (рис. 4). Результатом работы данной схемы является поток нулей и единиц на выходе компаратора, который затем пропускается через цифровой ФНЧ, в результате получается N-битный результат. ФНЧ на рис. 3. Объединен с «дециматором», устройством, снижающим частоту следования отсчетов путем их «прореживания».

Рис. 4. Сигма-дельта АЦП как следящая система

Ради строгости изложения, нужно сказать, что на рис. 3 изображена структурная схема сигма-дельта АЦП первого порядка. Сигма-дельта АЦП второго порядка имеет два интегратора и две петли обратной связи, но здесь рассматриваться не будет. Интересующиеся данной темой могут обратиться к [3].

На рис. 5 показаны сигналы в АЦП при нулевом уровне на входе (сверху) и при уровне Vref/2 (снизу).

Рис. 5. Сигналы в АЦП при разных уровнях сигнала на входе.

Более наглядно работу сигма-дельта АЦП демонстрирует небольшая программа, находящаяся тут: http://designtools.analog.com/dt/sdtutorial/sdtutorial.html.

Теперь, не углубляясь в сложный математический анализ, попробуем понять, почему сигма-дельта АЦП обладают очень низким уровнем собственных шумов.

Рассмотрим структурную схему сигма-дельта модулятора, изображенную на рис. 3, и представим ее в таком виде (рис. 6):

Рис. 6. Структурная схема сигма-дельта модулятора

Здесь компаратор представлен как сумматор, который суммирует непрерывный полезный сигнал и шум квантования.

Пусть интегратор имеет передаточную функцию 1/s. Тогда, представив полезный сигнал как X(s), выход сигма-дельта модулятора как Y(s), а шум квантования как E(s), получаем передаточную функцию АЦП:

То есть, фактически сигма-дельта модулятор является фильтром низких частот (1/(s+1)) для полезного сигнала, и фильтром высоких частот (s/(s+1)) для шума, причем оба фильтра имеют одинаковую частоту среза. Шум, сосредоточенный в высокочастотной области спектра, легко удаляется цифровым ФНЧ, который стоит после модулятора.

Рис. 7. Явление «вытеснения» шума в высокочастотную часть спектра

Однако следует понимать, что это чрезвычайно упрощенное объяснение явления вытеснения шума (noise shaping) в сигма-дельта АЦП.

Итак, основным достоинством сигма-дельта АЦП является высокая точность, обусловленная крайне низким уровнем собственного шума. Однако для достижения высокой точности нужно, чтобы частота среза цифрового фильтра была как можно ниже, во много раз меньше частоты работы сигма-дельта модулятора. Поэтому сигма-дельта АЦП имеют низкую скорость преобразования.

Они могут использоваться в аудиотехнике, однако основное применение находят в промышленной автоматике для преобразования сигналов датчиков, в измерительных приборах, и в других приложениях, где требуется высокая точность. но не требуется высокой скорости.

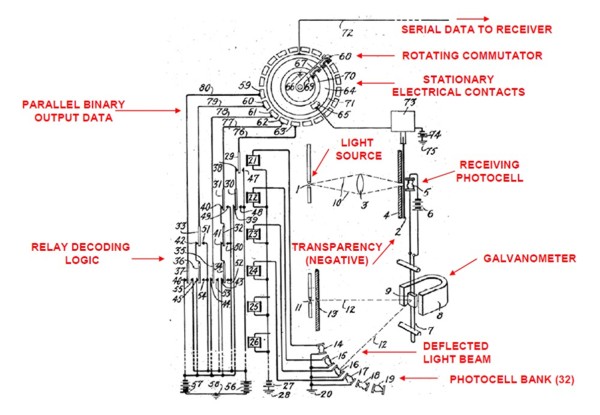

Самым старым упоминанием АЦП в истории является, вероятно, патент Paul M. Rainey, «Facsimile Telegraph System,» U.S. Patent 1,608,527, Filed July 20, 1921, Issued November 30, 1926. Изображенное в патенте устройство фактически является 5-битным АЦП прямого преобразования.

Рис. 8. Первый патент на АЦП

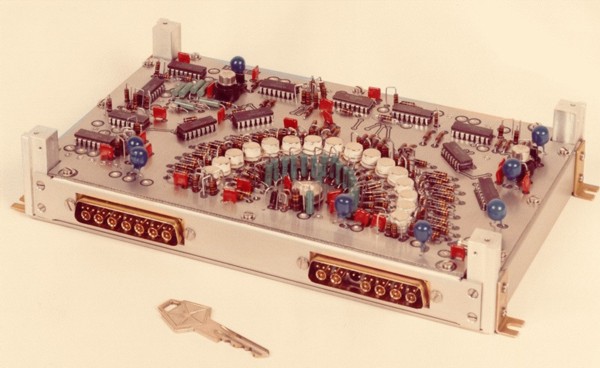

Рис. 9. АЦП прямого преобразования (1975 г.)

Устройство, изображенное на рисунке, представляет собой АЦП прямого преобразования MOD-4100 производства Computer Labs, 1975 года выпуска, собранный на основе дискретных компараторов. Компараторов 16 штук (они расположены полукругом, для того, чтобы уравнять задержку распространения сигнала до каждого компаратора), следовательно, АЦП имеет разрядность всего 4 бита. Скорость преобразования 100 MSPS, потребляемая мощность 14 ватт.

На следующем рисунке изображена продвинутая версия АЦП прямого преобразования.

Рис. 10. АЦП прямого преобразования (1970 г.)

Устройство VHS-630 1970 года выпуска, произведенное фирмой Computer Labs, содержало 64 компаратора, имело разрядность 6 бит, скорость 30MSPS и потребляло 100 ватт (версия 1975 года VHS-675 имела скорость 75 MSPS и потребление 130 ватт).

25.4. Каналы АЦП

Чтобы упростить использование модуля АЦП, у него предусмотрено четыре отдельных регистра управления мультиплексорами, каждому из которых соответствует свой регистр результата. Регистровая пара мультиплексора/результата называется каналом АЦП (см. рисунок 25.1). Каждый канал АЦП раздельно настраивается на измерение различных входных источников, использует различные условия запуска преобразования, события и прерывания. Результат преобразования запоминается в разных регистрах результата.

Вот один из вариантов использования каналов АЦП: одна пара регистров мультиплексора/результата настроена на выполнение несимметричных измерений, запускаемых сигналом события, другая пара регистров мультиплексора/результата отвечает за дифференциальное измерение, инициированное другим сигналом события и, наконец, две оставшихся пары регистров измеряют еще два входных источника под управлением программы.

Все каналы АЦП для выполнения преобразования используют один и тот же АЦП, однако, благодаря его конвейерной архитектуре, новое преобразование можно запускать по каждому циклу синхронизации АЦП. Это означает, что одновременно и независимо, не требуя изменений настроек мультиплексора, могут прогрессировать несколько преобразований.

Результат преобразований каждого канала сберегается в отдельном регистре. По мере выполнения очередных преобразований в этом канале, обновляться будет именно его регистр результата, не затрагивая прочие регистры результата. Благодаря такому механизму преобразований, снижается сложность программы, а различные программные модули получают возможность начать преобразования и считать их результат полностью независимого друг от друга.

25.5. Выбор опорного напряжения

В качестве опорного напряжения АЦП (VREF) можно выбрать следующие напряжения:

Рисунок 25.8. Выбор опорного напряжения АЦП

25.6. Результат преобразования

АЦП можно настроить на работу в знаковом или беззнаковом режиме. Данная настройка является глобальной и, таким образом, распространяется на весь модуль АЦП и на все его каналы.

Если какой-либо из входов АЦП настроен на дифференциальное измерение, необходимо использовать знаковый режим. В беззнаковом режиме возможно измерение только внешних или внутренних несимметричных сигналов.

Результат аналогово-цифрового преобразования (RES) записывается в один из регистров результата. Передаточная функция АЦП имеет следующий вид:

Программно можно задать разрешающую способность результата 8 или 12 бит. Преобразование с более низкой разрешающей способностью выполняется быстрее. О том, как рассчитать задержку распространения см. в 25.9 «Синхронизация и временная диаграмма преобразования АЦП».

Регистры результата являются 16-битными. 8-битный результат всегда представляется в 16-битном регистре результата с правым выравниванием. Правое выравнивание означает, что 8 младших бит результата помешаются в младший байт регистра результата. 12-битный результат может быть представлен как с левым, так и с правым выравниванием. Левое выравнивание означает, что 8 старших бит результата помещаются в старший байт регистра результата.

Когда АЦП работает в знаковом режиме, старший бит результата является битом знака. В 12-битном режиме с правым выравниванием, бит знака (бит 11) копируется во все неиспользуемые старшие биты, т.е. биты 12…15. Это необходимо для того, чтобы хранящееся в регистре результата 16-битное значение автоматически воспринималось в программе, как 16-битное знаковое значение. Аналогичным образом, в 8-битном режиме бит знака (бит7) копируется во все биты старшего байта.

На рисунках 25.9…25.11 представлены входные диапазоны и представление 12-битного результата с правым выравниванием для различных входов.

Рисунок 25.9. Знаковый дифференциальный вход с усилением: входной диапазон и представление результата

Рисунок 25.10. Знаковый несимметричный внешний или внутренний вход: входной диапазон и представление результата

Рисунок 25.11. Беззнаковый несимметричный внешний или внутренний вход: входной диапазон и представление результата

25.7. Функция сравнения

Модуль ADC поддерживает функцию 12-битного сравнения. Для хранения 12-битного значения, которое соответствует аналоговому пороговому напряжению, предусмотрен регистр сравнения модуля ADC. Каждый из каналов ADC можно настроить на автоматическое выполнение сравнения результата преобразования с заданным 12-битным значением и генерацию прерывания или события в случае, если результат преобразования больше или меньше порога.

Все четыре канала ADC работают с одним и тем же регистром сравнения.

25.8. Запуск преобразования

Перед тем как запустить преобразование, необходимо выбрать требуемые входные источники для одного или более каналов ADC. Запустить преобразование в канале ADC можно либо программной записью единицы в бит запуска преобразования канала ADC, либо событием системы событий. Допускается одновременная запись бит запуска преобразования нескольких каналов ADC или использование одного и того же события для одновременного запуска преобразований в нескольких каналах ADC. Используя эту возможность, можно добиться сканирования нескольких или всех каналов ADC под управлением одного события.

25.9. Синхронизация и временная диаграмма преобразования АЦП

Рисунок 25.12. Предделитель АЦП

Максимальная частота преобразований АЦП равна частоте его синхронизации (fADC). АЦП может инициировать новое преобразование по каждому циклу синхронизации АЦП.

Частота преобразования = fADC

Задержка распространения АЦП определяется по выражению:

Задержка распространения = (1 + 0.5·RES + GAIN)/fADC,

Несмотря на то, что задержка распространения составляет более одного цикла синхронизации АЦП, конвейерная архитектура исключает любые ограничения на соотношение частоты преобразования и задержки распространения.

25.9.1. Одиночное преобразование без усиления

На рисунке 25.13 показана временная диаграммы работы АЦП при выполнении одиночного преобразования без усиления. Для фактического запуска преобразования АЦП необходимо, чтобы записанный бит запуска преобразования или событие запуска преобразования (START), удерживалось в активном состоянии минимум один цикл синхронизации УВВ перед началом цикла синхронизации АЦП (см. залитую серым цветом наклонную область на графике START).

Выборка источника аналогового входа выполняется за первую половину первого цикла и, таким образом, время выборки всегда равно половине периода синхронизации АЦП. Снижение или увеличение частоты синхронизации АЦП оказывает прямое влияние на величину времени выборки.

Старший бит результата преобразования оцифровывается первым, а на оцифровку остальных бит затрачивается 3 (8-битное преобразование) или 5 (12-битное преобразование) циклов синхронизации АЦП. На преобразование одного бита затрачивается половина периода синхронизации АЦП. По ходу последнего цикла выполняется подготовка результата преобразования, а затем устанавливается флаг прерывания. Результат доступен для считывания в регистре результата.

Рисунок 25.13. Временная диаграмма одиночного преобразования без усиления

25.9.2. Одиночное преобразование с усилением

На рисунке 25.14 показана временная диаграмма работы АЦП при выполнении одиночного преобразования с усилением. Как было показано в 25.2 «Обзор» усилительный каскад расположен перед АЦП. Это означает, что вначале выполняются выборка и усиление источника аналогового входа в усилительном каскаде, а уже затем АЦП выполняет преобразование выборки усиленного аналогового напряжения. По сравнению с одиночным преобразованием без усиления здесь требуется один дополнительный цикл синхронизации АЦП (между START и выборкой АЦП) для выборки и усиления в усилительном каскаде. Время выборки в усилительном каскаде равно половине цикла синхронизации АЦП.

Рисунок 25.14. Временная диаграмма одиночного преобразования с усилением

25.9.3. Одиночные преобразования в двух каналах АЦП

На рисунке 25.15 показана временная диаграмма работы АЦП при выполнении одиночных преобразований в двух каналах АЦП. Благодаря конвейерной архитектуре АЦП, второе преобразование можно запустить в следующем цикле синхронизации АЦП после запуска первого преобразования. В этом примере оба преобразования запускаются одновременно, но фактически канал 1 АЦП (CH1) не запускается, пока не завершится выборка и преобразование старшего бита в канале 0 (CH0).

Рисунок 25.15

25.9.4. Одиночные преобразования в двух каналах АЦП и с усилением в канале 0

На рисунке 25.16 показана временная диаграмма преобразований в двух каналах АЦП и с усилением в канале 0. Поскольку усилительный каскад добавляет один цикл на выборку и усиление, выборка канала 1 также задерживается на один цикл синхронизации АЦП вплоть до завершения выборки и преобразования старшего бита в канале 0.

Рисунок 25.16. Временная диаграмма одиночных преобразований в двух каналах АЦП с усилением в канале 0

25.9.5. Одиночные преобразования в двух каналах АЦП и с усилением в канале 1

Временная диаграмма преобразований в двух каналах АЦП и с усилением в канале 1 показана на рисунке 25.17.

Рисунок 25.17. Временная диаграмма преобразований в двух каналах АЦП

25.9.6. Автоматический режим с усилением в двух каналах АЦП

Рисунок 25.18. Временная диаграмма АЦП в автоматическом режиме

Каналы АЦП

Добро пожаловать на ChipTuner Forum.

Опции темы

syetra

АЦП – аналого-цифровой преобразователь.

Все аналоговые сигналы – напряжение от датчиков температуры, положения дроссельной заслонки, остаточного содержания кислорода в отработанных газах, расхода воздуха, для обработки программой управления двигателем должны быть переведены в цифровой вид. Напряжение АЦП есть напряжение от датчиков на входе микросхемы – АЦП. Диапазон входного напряжения АЦП обычно от 0 В до +5 В. Большинство сигналов датчиков лежит в этом диапазоне, это например напряжение от ДМРВ, ДПДЗ, ДТОЖ.

Однако напряжение питания контроллера больше 5 вольт, а именно от 8 до 16 и более в случае поломки генератора, и в этих условиях необходимо сохранить приемлемую работу двигателя. Это в первую очередь изменение времени открытия форсунок и времени накопления катушкой зажигания энергии для формирования искры. Эти калибровки заложены в программе контролера, напряжение питания делится например на 4, и вместо 16 вольт на входе АЦП получаем 4. На «4» я примерно написал, на сколько на самом деле делится в Микасе7.1 например – не помню. Так вот, получили на входе АЦП 4 вольта. Но для диагностического сканера в графе «напряжение бортовой сети» мы прочитаем 16 вольт. Ну во первых есть протокол, где на запрос оборотов двигателя контроллер высылает один байт, а программа диагностики должна этот байт на что-то умножить, с чем-то сложить и получится число оборотов в десятичном виде. Так и показания АЦП и напряжение могут совпадать, а могут отличаться. Иногда это удобно.