криптографический сопроцессор что такое

Импортозамещение должно снизить потребность в чипах производства этой компании

Структура, научно-технический центр «Атлас», указывает в документации, что российский продукт может быть использован в рамках импортозамещения, как альтернатива системе от Freescale Semiconductor на кристалле P2020NSN2 и криптографического сопроцессора С291, пишет Cnews. Отечественный чип начали разрабатывать в ноябре 2015 года, а закончили — в ноябре 2017. Стоимость заказа составила 240 млн рублей.

Сообщается, что контракт с «Атласом» подписали по итогам конкурса на выполнение тематических опытно-конструкторских работ (ОКР) в рамках подпрограммы повышения конкурентоспособности отечественной промышленности «Ускоренное развитие оборонно-промышленного комплекса». Конкурентом «Атласа» выступает Научно-исследовательский институт системных исследований Российской академии наук.

«В результате выполнения ОКР разработана специализированная однокристальная ЭВМ, предназначенная для выполнения криптографических операций в соответствии с государственными стандартами. Работа выполнена в полном объеме технического задания, в установленные государственным контрактом сроки и принята государственной комиссией», — заявили в пресс-службе Минпромторга.

Что касается самого заказа, то «Атлас» выполнял работу по созданию доверенной специальной сверхбольшой интегральной схемы (СБИС) для построения средств криптографической защиты информации, обладающей повышенным быстродействием, малым энергопотреблением и встроенной подсистемой хранения ключей — аппаратного криптографического модуля. Масса чипа должна была составить не более 20 граммов, собственные резонансные частоты не должны быть ниже 100 Гц. Потребляемая мощность без подключенных внешних устройств — 25 Вт.

Готовая СБИС предназначалась для вычисления цифровой подписи по алгоритму ГОСТ 34.10 для кривой с модулем 512 бит на уровне не менее 2500 операции в секунду, вычисление значения хэш-функции по алгоритму ГОСТ 34.11 — не менее 2500 мбит/с, шифрование данных по алгоритму ГОСТ 28147 — не менее 2500 Мбит/с. Стоит отметить, что сама разработка — секретная, при выполнении всех работ «Атлас» должен был руководствоваться требованиями закона о гостайне. Кроме того, компания была обязана соблюдать требования о порядке обращения со служебной информацией ограниченного распространения в федеральных органах исполнительной власти.

«Научно-технический центр „Атлас“» ведет историю с 1951 года. Изначально организация была опытным заводом, разрабатывавшим новые технические средства службы специальной связи. В начале 1990-х компания получила новые задания. Например, было освоено такое направление, как создание защищенных информационно-телекоммуникационных систем, создавались новые методы защиты компьютерной информации, плюс средства защиты данных при передаче по каналам связи.

Не так давно на Geektimes сообщалось и о другой российской разработке — отечественном процессоре «Байкал», который поступает в розничную продажу. Начало продаж запланировано на первый квартал 2018 года. Тогда в розничные магазины станут поступать первые партии отечественных чипов. Стоит отметить, что процессоры будут продавать в составе оценочных плат семейства БФК 3.1 (блок функционального контроля).

Перед покупкой процессор можно протестировать бесплатно — в лаборатории отечественной электроники на базе ЦОДа ВМК МГУ имени М.В. Ломоносова. Здесь можно оценить производительность отечественного чипа, а также решений на его основе. Процессор, насколько известно, создается по архитектуре MIPS (Microprocessor without Interlocked Pipeline Stages). Она соответствует концепции RISC, то есть для процессоров с сокращенным набором команд.

Средства обеспечения безопасности

Криптографический сопроцессор PCIXCC

Криптографический акселератор PCICA

Поскольку устройства PCICA участвуют только в операциях, связанных с обработкой открытых ключей, они не имеют защищенного конструктивного исполнения, как это принято в PCIXCC. В конфигурацию систем zSeries может быть включено максимум шесть акселераторов ( по два на один конструктив ввода/вывода) вместе с четырьмя PCIXCC. При этом суммарное количество устройств этих типов в z990 не должно превышать восьми. В этих пределах допускается любое сочетание используемых PCICA и PCIXCC, что позволяет клиентам (заказчикам систем) гибко масштабировать структуру обеспечения защищенного электронного бизнеса.

Каждое устройство PCICA имеет до двух плат акселераторов, встраиваемых в модуль адаптера, и может быть распределено на любой логический раздел, определенный в системе (табл. 4.6).

| Тип адаптера | Максимальное число устройств на сервер | Число криптографических сопроцессоров в устройстве | Максимальное число криптографических сопроцессоров на сервер | Число криптографических доменов на сопроцессор | Число логических разделов на сервер (определенных/активных) |

| PCICA | 6 | 2 | 12 | 16 | 30/30 |

| PCIXCC | 4 | 1 | 4 | 16 | 30/30 |

В таблице 4.7. приведены данные, позволяющие оценить основные функциональные возможности криптографических устройств системы z990.

| Функция, атрибут | CPACF | PCIXCC | PCICA |

| Поддержка z/OS приложений с использованием ICSF | + | + | + |

| Шифрование/дешифрация с использованием алгоритма секретного ключа | + | ||

| Высокоскоростное установление SSL-сессии | + | ||

| Выполнение высокоскоростного симметричного шифрования (открытый ключ ) | + | ||

| Выполнение высокоскоростного асимметричного шифрования (открытый ключ ) | + | ||

| Физически включен в состав центрального процессора (ЦП) | + | ||

| Требует активации CPACF | + | + | + |

| Требует активного состояния ICSF | + | + | |

| Участие в обеспечении конфиденциальности данных (шифрование/дешифрация) | + | + | |

| Участие в обеспечении целостности данных (хэширование, аутентификация сообщений) | + | + | |

| Требует загрузки системных мастер-ключей | + | ||

| Поддержка функций протокола SSL | + | + | + |

| Операционная система | CPACF | PCIXCC | PCICA |

| z/OS v.1. и выше | + | + | + |

| z/OS v.1.3 | + | + | + |

| z/OS v.1.2 | + | + | + |

| OS/390 v.2.10 | + | + | + |

| z/VM v.4.2 и выше | + | ||

| z/VM v.4.2 и выше (только для Linux Guests) | + | ||

| z/VM v.3.1 | + | ||

| Linux 2.4.7 для Zseries | + | ||

| VSE/ ESA v.2.7 и | |||

| IBM TCP/IP для VSE/ ESA v.1.5 | + |

Система базовых криптографических сервисов z/OS обеспечивает доступ приложений к аппаратным средствам криптографии тремя путями с использованием продуктов (рис. 4.18):

Что такое ЭКЛЗ и как это работает

Предприниматели, использующие в своей деятельности контрольно-кассовый аппарат, обязательно имеют дело с устройством ЭКЛЗ, призванном контролировать производимые с помощью кассы финансовые операции.

Каковы нюансы использования ЭКЛЗ, в чем могут содержаться ее «подводные камни» для предпринимателей, а также какие изменения, связанные с ее применением, принесут бизнесменам правительственные нововведения, вы узнаете, прочитав этот материал.

Аббревиатура и смысл устройства

ЭКЛЗ расшифровывается как «электронная контрольная лента защищенная». Это механизм, который несколько сродни «черному ящику»: он обеспечивает скрытую от вмешательства извне защиту фискальных данных контрольно-кассовой машины и их долговременное хранение. Иными словами, на ЭКЛЗ записываются все операции, производимые на данном кассовом аппарате:

Устройство состоит из 3 элементов.

ВАЖНО! ЭКЛЗ энергетически автономна, что обеспечивает хранение данных в любых условиях.

Секретный КПК

Этот код автоматически вычисляется сопроцессором для каждого пробитого чека и отображается на нем в виде уникального номера (то есть каждый чек получает свой собственный код).

Предназначение КПК – дополнительный налоговый контроль. Налоговый инспектор может, сличив КПК с данными чека, определить их взаимное соответствие и легко вычислить манипуляции с ЭКЛЗ, если они имели место. Таким образом, нерадивый предприниматель, попытавшийся обнулить выручку для уменьшения налогового бремени, будет выведен на чистую воду.

К СВЕДЕНИЮ! Любой покупатель, получивший кассовый чек, может удостоверить его подлинность, проверив КПК на официальном сайте налоговой инспекции или специальных информационных ресурсах.

Как происходит кодирование информации в КПК

Когда кассир пробивает чек, в недрах контрольно-кассового аппарата происходит сложная работа, обеспечивающая фиксацию и хранение сведений о произведенной операции. Этот процесс осуществляется в несколько этапов.

ЭКЛЗ – точный прибор

Установка и замена ЭКЛЗ с их активацией производится техническим специалистом.

ЭКЛЗ является одноразовым прибором, смысл его работы в том, что данные не поддаются внешней коррекции, поэтому ошибка при активации недопустима. Если она допущена техническим специалистом или самим предпринимателем (кассиром), ЭКЛЗ становится непригодным к использованию.

Данные, которые может предоставить ЭКЛЗ

Вместо устаревших бумажных лент, которые требовалось хранить несколько лет, что не позволяло обнаружить в бумажном хаосе нужную информацию, электронная защищенная лента позволяет легко выдать по запросу необходимую информацию:

Из истории ЭКЛЗ

ЭКЛЗ не всегда присутствовала в составе контрольно-кассовых механизмов. До 2000 года вместо нее использовалась фискальная память, оказавшаяся не очень надежным хранилищем для таких данных. Умелые хакеры придумали интерфейс, позволяющий вмешиваться в корректировку данных фискальной памяти, даже не вскрывая заводских пломб. Потерпевшая фиаско идея нуждалась в обновлении.

Федеральное агентство правительственной связи и информации, действующее по инициативе Президента РФ, разработало новую концепцию сохранения фискальных данных ККМ, основанную на криптографии, то есть формировании защитного кода. Опытный образец прошел испытания, и уже в следующем, 2001 году был утвержден Государственной Межведомственной Экспертной комиссией, а в 2002 году начато серийное производство ЭКЛЗ.

С 1 октября 2004 года использование ЭКЛЗ в кассовых аппаратах стало обязательным для всех предпринимателей. Отсутствие ЭКЛЗ стало считаться крупной провинностью, караемой серьезным штрафом.

ЭКЛЗ уйдет в прошлое?

В 2016 году Правительством РФ принят ряд законодательных новшеств, касающихся использования контрольно-кассовых аппаратов. 03.06.2016 года Президентом был подписан закон 54-ФЗ «О применении контрольно-кассовой техники», призванный полностью изменить многие устаревшие способы регистрации выручки и налоговых отчетов о ней. Современные технологии меняют принцип хранения данных на их немедленную передачу онлайн.

Главные грядущие изменения

ОБРАТИТЕ ВНИМАНИЕ! Некоторых видов деятельности изменения не коснутся – с их перечнем можно ознакомиться на официальных налоговых ресурсах.

Когда все изменится

Закон уже вступил в силу, но пока он не обеспечен соответствующим количеством техники, поэтому переход на новые правила будет постепенным.

Если контрольно-кассовый аппарат предпринимателя зарегистрирован в налоговой инспекции до 1 февраля 2017 года, его можно без ограничений и каких-либо санкций использовать до 1 июля 2017 года. Далее старую кассу придётся обновлять и проходить перерегистрацию – разумеется, за счет самого предпринимателя. Кстати, мы уже писали об этом в новостном материале «сроки перехода на онлайн-кассы». Там все даты вынесены в таблицу, что наглядно демонстрирует, когда именно нужно готовиться менять оборудование.

Работа с криптопроцессором. Программирование OTP

ВВЕДЕНИЕ

СТРУКТУРА ВЗАИМОДЕЙСТВИЯ. ШЛЮЗ

На рисунке 1 приведена общая схема микроконтроллера, которая показывает, что всё взаимодействие между ядрами M4 и защищенным M0 осуществляется через шлюз обмена данных.

Рисунок 1 – Структурная схема микроконтроллера 1986ВК01

Стоит отметить, что на данной схеме не отражены отладочные интерфейсы. Как отмечено было ранее, в защищенном криптомодуле реализован отладочный интерфейс SWD. Он доступен на следующих портах ввода – вывода:

Но в «Release» варианте программы пользоваться отладчиком возможности нет, поэтому в первую очередь рассмотрим взаимодействие через шлюз. Шлюз представляет собой:

16 входных/выходных регистров (8 входных и 8 выходных. Следовательно, входной с одной стороны является выходным с другой),

2 FIFO данных: от открытого ядра к защищённому, и от защищённого ядра к открытому, шириной данных 32 бита и объёмом 16 слов.

Реализовано по 3 служебных регистра: для FIFO и для входных/выходных регистров. Они необходимы для контроля и настройки взаимодействия обмена данными по шлюзу. Подробная карта регистров блока шлюза представлена в таблице 1.

Таблица 1 – Карта регистров блока Шлюза

| Открытая сторона M4 | Название регистра | Закрытая сторона M0 | ||

| Доступ | Описание регистра | Описание регистра | Доступ | |

| w/o | Регистр записи во входное FIFO к защищённой стороне. | OP_FIFO_OP_TO_SF | Регистр чтения из входного FIFO от открытой стороны. | r/o |

| r/o | Регистр чтения из выходного FIFO от защищённой стороны. | OP_FIFO_SF_TO_OP | Регистр записи в выходное FIFO к открытой стороне. | w/o |

| r/w | Регистр задания контрольных уровней заполненности FIFO. | OP_FIFO_LEVELS | Регистр задания контрольных уровней заполненности FIFO. | r/w |

| r/w | Регистр задания маски разрешения источников запроса прерывания FIFO. | OP_FIFO_INT_MASK | Регистр задания маски разрешения источников запроса прерывания. | r/w |

| r/w | Регистр индикации и очистки источников запроса прерывания FIFO. | OP_FIFO_INT_SOURCE | Регистр индикации и очистки источников запроса прерывания. | r/w |

| r/w | Входной регистр. | OP_REG_0 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_1 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_2 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_3 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_4 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_5 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_6 | Выходной регистр. | r/o |

| r/w | Входной регистр. | OP_REG_7 | Выходной регистр. | r/o |

| r/o | Выходной регистр. | OP_REG_8 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_9 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_10 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_11 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_12 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_13 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_14 | Входной регистр. | r/w |

| r/o | Выходной регистр. | OP_REG_15 | Входной регистр. | r/w |

| r/o | Регистр статуса занятости входных регистров. | OP_REGS_BUSY | Регистр статуса занятости входных регистров. | r/o |

| r/w | Регистр задания маски разрешения источников запроса прерывания REG_x. | OP_REGS_INT_MASK | Регистр задания маски разрешения источников запроса прерывания REG_x. | r/w |

| r/w | Регистр индикации и очистки источников запроса прерывания REG_x. | OP_REGS_INT_SOURCE | Регистр индикации и очистки источников запроса прерывания REG_x. | r/w |

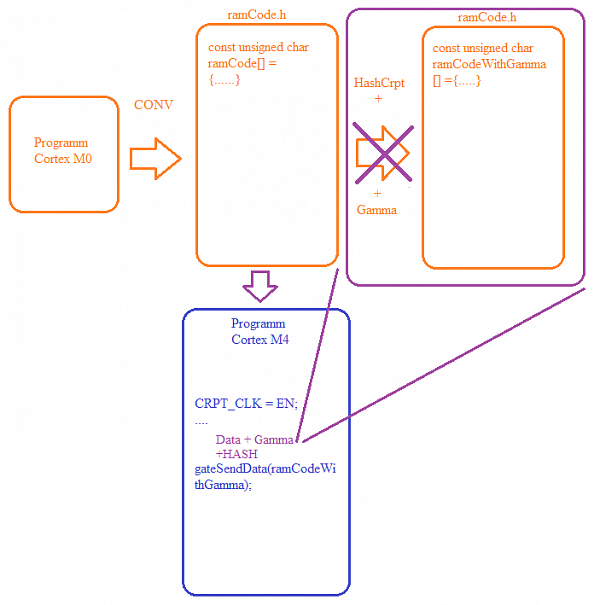

Общий алгоритм добавления исполняемой программы в память криптографического сопроцессора представлен на рисунке 2.

Подготовить программу для работы сопроцессора M0.

Конвертировать программу в массив данных.

К этому массиву необходимо добавить Hash и наложить гамму.

После чего новый массив данных уже можно использовать в программе для ядра M4.

В основной программе для открытого ядра необходимо разрешить тактирование M0, после чего ядро M4 может приступить к передаче зашифрованных данных через шлюз в ядро M0.

Предварительно систему криптомодуля необходимо проинициализировать, а именно, записать серийный номер, записать гамму для расшифровки получаемой программы. Этот процесс осуществляется с помощью UART – загрузчика, выведенного на выводы:

PD[2] / UARTTX

PD[3] / UARTRX

СТАРТ И ИНИЦИАЛИЗАЦИЯ КРИТПОЯДРА

После старта загрузочная программа ядра Cortex-M0 начинает выполнять чтение статуса из OTP памяти по определенному адресу (0x1010C0000) и анализирует его:

если статус = 0x0000A55A, загрузчик приступает к процедуре инициализации OTP;

если статус = 0x75A9A55A, загрузчик понимает, что OTP инициализирована и приступает к процедуре обработки данных, полученных через шлюз от ядра M4.

Таким образом, есть 3 фазы работы встроенного загрузчика:

Выполняется проверка целостности серийного номера и его отправка в незащищённое ядро.

Выполняется проверка целостности серийного номера и гаммы, после чего серийный номер отправляется через шлюз в незащищённое ядро.

По готовности в регистрах шлюза выставляется флаг готовности. Прочитав этот флаг программное обеспечение незащищённого ядра должно загрузить в шлюз зашифрованную прошивку.

Загрузчик защищённого ядра проверяет целостность зашифрованной прошивки, сравнивая её CRC32. Если проверка выполнена успешна, то происходит расшифровывание прошивки в оперативной памяти путём её сложения с гаммой по модулю 2.

Целостность расшифрованной прошивки определяется путём расчёта и сравнения с расшифрованным значения хэш-функции RIPEMD-160.

Если целостность прошивки подтверждена, выставляется флаг готовности и управление передаётся расшифрованной прошивке в оперативной памяти

Рассмотрим каждую процедуру по отдельности.

Преинициализация

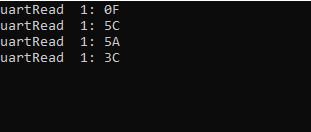

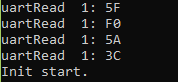

По сути, данная процедура запускается всегда, когда OTP-память пустая. Первым этапом происходит настройка UART:

UART настраивается на скорость 9600 бод при условии, что частота тактирования микроконтроллера 8 МГц.

Ниже приведены все расшифровки статусов загрузчика:

// Base CM0 UART/GATE statuses

#define CM0_OK ((CM0_STATUS)0x3C5A0000)

#define CM0_FAIL ((CM0_STATUS)0xC3A50000)

#define CM0_PREINIT_READY ((CM0_STATUS)(0x5C0F | CM0_OK))

#define CM0_PREINIT_DONE ((CM0_STATUS)(0xC535 | CM0_OK))

#define CM0_PREINIT_FAIL ((CM0_STATUS)(0x533A | CM0_FAIL))

#define CM0_INIT_READY ((CM0_STATUS)(0xF05F | CM0_OK))

#define CM0_INIT_DONE ((CM0_STATUS)(0xC335 | CM0_OK))

#define CM0_INIT_FAIL ((CM0_STATUS)(0xFC3A | CM0_FAIL))

#define CM0_GAMMA_READY ((CM0_STATUS)(0x0A59 | CM0_OK))

#define CM0_WORK_READY ((CM0_STATUS)(0xF535 | CM0_OK))

#define CM0_WORK_DONE ((CM0_STATUS)(0xA50A | CM0_OK))

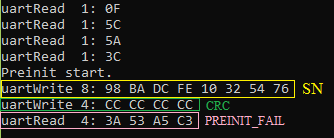

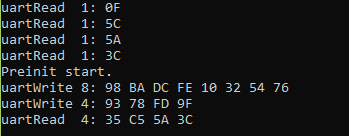

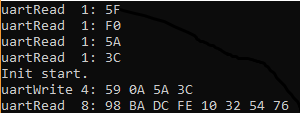

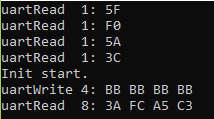

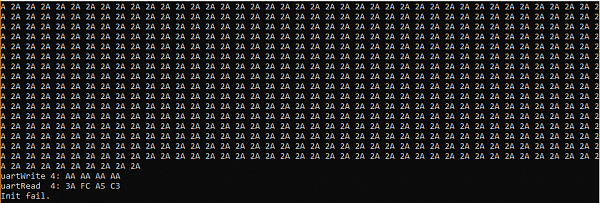

Затем ядро M0 ожидает приём по UART 8 байт серийного номера и 4 байта контрольной суммы CRC данного номера. После получения этих данных МК самостоятельно рассчитывает CRC от полученного серийного номера и сравнивает со значением, полученными по UART. В случае если значения не сошлись, то загрузчик возвращает статус CM0_PREINIT_FAIL. На рисунке 4 показан пример ввода серийного номера SN и некорректно рассчитанной к нему контрольной суммы CRC, в результате чего получен ожидаемый статус о неудачной процедуре преинициализации.

Рисунок 4 – Загрузчик вернул статус неудачной преинициализации

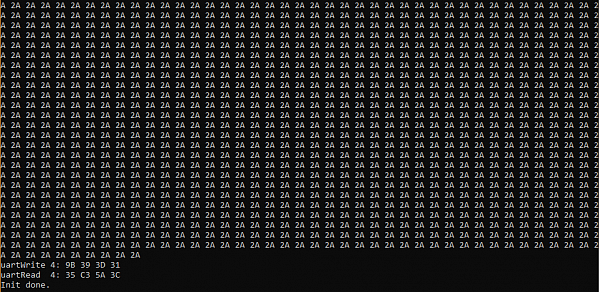

После возвращения статуса PREINIT_FAIL микроконтроллер зависает в бесконечном цикле, повторно дублируя данный статус в шлюз к ядру M4 через 15 регистр. Требуется выполнить сброс, чтобы повторно провести процедуру преинициализации с корректно рассчитанной контрольной суммой. При отправке корректной контрольной суммы микроконтроллер выдаст статус PREINIT_DONE – рисунок 5.

Рисунок 5 – Получение статуса об успешной преинициализации

После выдачи статуса об успешной процедуре преинициализации микроконтроллер записывает во внутреннюю OTP-память статус 0x0000A55A, и CRC, рассчитанное от статуса и серийного номера, после чего вновь зависает. Важно отметить, что в результате успешной или неуспешной процедуры преинициализации микроконтроллер безальтернативно зависает. Разница состоит в том, что, когда процедура выполняется успешно, происходит запись статуса в OTP-память, который анализируется при старте загрузчика. То есть наличие данных 0x0000A55A в статусе позволяет перейти к процедуре инициализации.

Инициализация

После сброса процессор, прочитав измененный статус во внутренней OTP-памяти, приступил к процедуре инициализации, сообщив об этом по UART, выдавая статус INIT_READY – рисунок 6. Дополнительно в 8 и 9 регистры шлюза загрузчик отправил серийный номер, записанный в его OTP-памяти во время преинициализации.

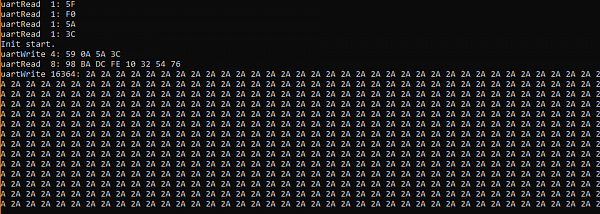

Затем необходимо передать загрузчику информацию о том, что гамма сформирована, то есть отправить статус GAMMA_READY. В ответ ожидается серийный номер, записанный в OTP-память на предыдущем этапе – рисунок 7. В случае же некорректной передачи статуса, в ответ поступит сообщение INIT_FAIL – рисунок 8.

После успешной выдачи серийного номера микроконтроллер ожидает принять гамму размером 16364 байта. Это обязательное условие загрузчика. В рассматриваемом случае, к примеру, в качестве гаммы было выбрано число 42.

После принятия гаммы загрузчик микроконтроллера ожидает получить контрольную сумму CRC для переданной гаммы, после чего её проверяет. Если контрольная сумма не сошлась, в ответ загрузчик вернет статус INIT_FAIL – рисунок 10.

В случае передачи корректной CRC микроконтроллер приступает к прошивке гаммы во внутреннюю OTP-память, затем изменяет и переписывает в памяти OTP основной статус, который опрашивается при старте процессора на OTP_INIT 0x75A9A55A. После чего рассчитывает новое значение CRC от статуса, серийного номера и гамма, и выдает в UART статус INIT_DONE, что свидетельствует об окончании процесса инициализации – рисунок 11. И, как было отмечено ранее, микроконтроллер опять зависнет даже в случае успешной инициализации и вновь потребует сброса.

После окончания процесса инициализации при последующем сбросе, загрузчик прочитает статус из своей памяти OTP_INIT 0x75A9A55A, что говорит о том, что он готов принимать зашифрованную по прописанной гамме программу, для последующей расшифровки и записи.

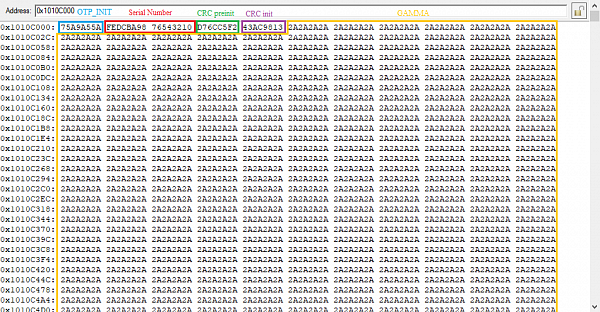

Если подключиться с помощью отладчика к ядру M0, то можно посмотреть, как выглядят записанные данные в OTP-памяти – рисунок 12.

ЗАПУСК ПРОГРАММЫ НА КРИПТОЯДРЕ

Подготовка

Алгоритм взаимодействия между ядрами с помощью шлюза приведен выше на рисунке 2. В рамках демонстрации рассмотрим его на конкретном примере: будем накладывать гамму и HASH на прошивку для ядра M0 внутри программы для M4. Это отображено на измененной схеме алгоритма на рисунке 13.

Запуск

К данной статье приложено два проекта:

1) Loader – проект с программой для ведущего ядра Cortex-M4, в котором разрешается тактирование криптоядра, а затем шифруется по гамма и передается через шлюз программа для исполнения ядром Cortex-M0;

2) CryptoHello – программа для исполнения ядром Cortex-M0.

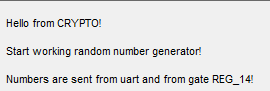

Во втором проекте (CryptoHello) конфигурируется модуль UART и отправляется приветствие. Затем включается блок генератора случайных чисел, который генерирует число и отправляет его всё по тому же UART, а также дублирует его в 14 регистр шлюза.

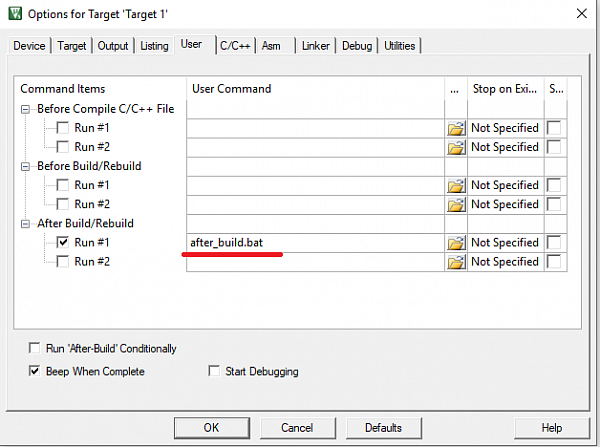

После того как программа для Cortex-M0 была написана, необходимо сгенерировать файл ramCode.h. В приложенном проекте после процесса компиляции выставлена опция запуска файла формата *.bat для генерации файла ramCode.h (рисунок 14).

То есть программа для исполнения ядром M0 была конвертирована в массив данных. Полученный файл ramCode.h необходимо добавить в проект для ядра Cortex-M4.

Теперь можно перейти к запуску первого проекта (Loader). Стоит вновь обратить внимание на разрешение тактирования криптоядра:

Затем в проекте происходит наложение HASH и Gamma на массив чисел из файла ramCode.h, который был добавлен в проект. После чего в основном цикле программы проверяется 15-ый регистр шлюза, куда криптоядро, как отмечено ранее, должно выставить статус WORK_READY.

Теперь ядро M0 готово принимать защищенную по гамма прошивку. Анализируя готовность, ядром M4 отправляется через шлюз подготовленный заранее код.

4 сек на частоте 8 МГц. Данное время тратится на отработку загрузчика.

Приложение 1. Алгоритм расчёта CRC

uint32_t crc32(uint32_t ctx, const uint8_t* buf, uint32_t sz)

<

ctx = ctx ^ 0xFFFFFFFF;

return ctx ^ 0xFFFFFFFF;

>

Приложение 2. Блокировка отладочного интерфейса криптоядра

Важной особенностью защищенной системы является отсутствие возможности проникнуть в неё извне. Одним из первостепенных механизмов защиты является блокировка отладочного интерфейса защищенной подсистемы. Блокировку целесообразно осуществлять после отладки приложения (пользовательской программы). Такая возможность в системе M0 есть. Реализуется она с помощью записи защитного слова в память OTP по адресу 0x10100000.

#define OTP_BASE ((uint32_t)0x10100000U)

#define OTP_MEM_BASE (OTP_BASE)

#define OTP_MEM ((uint32_t *)OTP_MEM_BASE)

OtpData* const gOtpMem = (OtpData*)OTP_MEM;

typedef struct

<

OtpUserData UData; /*

По данному адресу записывается SecurityWord = (0xFFFFFF #include «otpData.h»

if ( readOtpWord == SecurityWord)

uartWrite («\r\n JTAG is already blocked! \r\n», 30);

else

<

otpWrite(&gOtpMem->UData.Special, &SecurityWord, 1);

uartWrite («\r\n JTAG blocked! \r\n», 15);

>

.

>

Временная блокировка SWD-интерфейса криптоядра

Выводы CRPT_SWD совмещены с выводами PC[31:30], при этом после подачи тактирования на защищённую подсистему в регистре CRPT_CLK_CTRL (асинхронный тип регистра), выводы PC[31:30] полностью переходят под управление интерфейса SWD (Cortex-M0) и не могут управляться контроллером портов ввода-вывода и другими периферийными блоками из открытой подсистемы. На время отладки ПО, помимо блокировки SWD через OTP, есть возможность отключить в защищенной подсистеме интерфейс SWD, чтобы выводы PC[31:30] снова стали доступны для управления из открытой подсистемы. Для этого в ПО для Cortex-M0 необходимо сбросить бит 7 (DEBUG_EN) регистра SYS->CTRL:

(1

После сброса бита DEBUG_EN выводы PC[31:30] снова перейдут под управление открытой подсистемы (Cortex-M4F). Чтобы снова включить интерфейс SWD ядра Cortex-M0 необходимо выполнить сброс МК, программным способом установить бит DEBUG_EN для включения SWD нельзя.